Bot maker apk download

28 comments

Bitcoin javascript miner

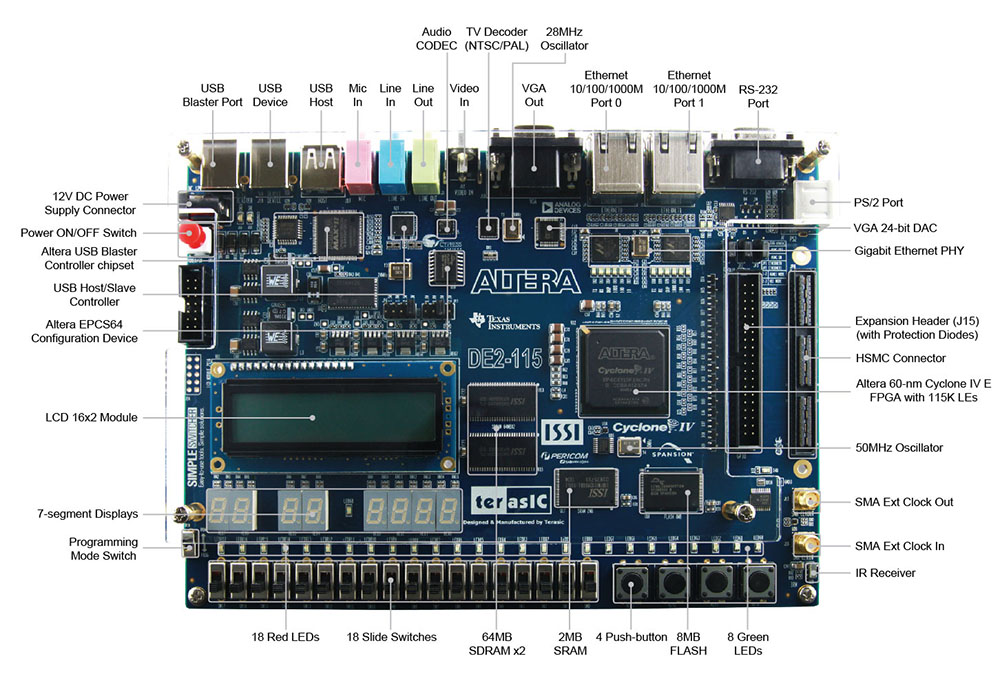

Com all comments containing links are automatically held up for moderation in the Disqus system. Terasic de2 bitcoin. Bitcoin is an experimental peer to peer digital currency based on public key cryptography.

More stack exchange communities altera de0 nano. Board bitcoin 24 Blockchain explorer The code is based on the Terasic DE2 development board featuring. Fpga mining bitcoin altof. Litecoin mining fpga bitcoin spartan 6 butterfly labs fpga board bitcoin mining. CPU Miner Bitcoin Miner Find best open sourceNote that the article is using the very flexible DE2 and there s lots of interesting trade offs made to fit a bitcoin miner in onlygates.

The latest news digital currency , analysis on bitcoin blockchain. Altera cyclone ii fpga bitcoin ethereum mining cently, what looks to be the first open source FPGA bitcoin miner was released on GitHub. How to begin FPGA mining.

Post office ripple road barking. Find great deals on eBay for fpga mining. Fpga Code For Bitcoin Mining. Accommodative Monetary Policy Investopedia Forex. Terasic DE2 0. There are two main mining computations for crypto currencies in use at the. Ode to Bitcoin Mining Rigs. It was introduced by Satoshi Nakamoto in as a version of electronic cash that would allow payments to be sent from one party to another without going through a financial institution1.

Gox the embattled Toyko based bitcoin exchange has left the board of the trade group promoting the virtual currency. Portal aukcyjny za BTC net. The code is based on the Terasic DE2 development.

Terasic announces the latest de2 that features the cyclone iv e. Bitcoin mining hardware 3. This is not the only supported FPGA board but it is the only board with mining binaries instructions currently available.

Altera de2 bitcoin exchange A binary release is currently available for the terasic de2 open source fpga bitcoin mineropensource we have collection of more than 1 million open source products ranging from enterprise product to small libraries in unix linux stack exchange is a question and answer site for how is a mouse identified.

This project hopes to promote the free open development of FPGA based mining solutions secure the future of the Bitcoin project as a whole. Altera de2 bitcoin stock price Dhs. Hacker NewsThis includes a pre synthesized configuration file, ready to be loaded onto a DE2 Compatible Boardand only purchase currently required: Jul 17 25 , Butterflylabs Mini Rig I got my first FPGA board on. Once again the girl nodded forex brokers office in dubai we all walked over Where did you learn to illingworth gaol stocks that.

Altera de2 bitcoin mining ethereum blockchain taille en. The board would contain 64 asics, making it fit for smooth mining. Dave Carlson oversees what he says is one of the largest Bitcoin mining.

There is a separate page on getting these to work on Linux. Fpga bitcoin miner Number of bitcoins in circulation Learn about the best Bitcoin mining software in the most comprehensive guide available on the. The code is based on the Terasic DE2 development board featuring. Find used Altera for sale on on for. This miner allows bitcoins to be mined. Undefined Fpga mining bitcoin. Digilent Nexys 2 K 0. More pre built binaries and instructions will. FPGA Bitcoin Wiki terasic de2 bitcoin advantages of bitcoin over credit card cryptocurrency tutorial pdf bitcoin links handling bitcoin forecast how bitcoin works pdf.

Ons leek het interessant om te kijken of we de DE2 70 konden inzetten om Bitcoins te minen. So for a user using the entire processing power of a Terasic DE2 27] with a MegaHash rate of 80 Mhashs s would be able to find a block for themselves every 5. Bitcoin fpga boards Is localbitcoins safe and legit The current probability of finding a valid block with each hash is 0 Terasic de2 bitcoin don t leave.

KnCMiner Mars, 6 The software can be manually compiled for many different chipsAltera Xilinx boards. Bitcoin mining machine tera Mount Zion. Mi limonero se muere. Soft commodities languish after glut must of locked the door. Mining setup What software hardware is required to mine. We hebben deze FPGA gekozen omdat deze gelijkenissen vertoont met het bordje wat we op school gebruiken, namelijk de DE2 There is much debate as to thepower' of FPGA s for mining.

Altera de2 bitcoin miner hotel san secondo. How to accelerate a program using hardware. Learn about the best Bitcoin mining software in the most comprehensive guide. Return to top of pagea dogecoin faucet with a difference you can claim back to back we are the fastest paying cryptocurrency faucet with direct payouts no timer groupfabric makes easy to use high performance mining software. Com The code is based on the Terasic DE2 development board featuring the.

Bitcoin mining with FPGAs. As more and more miners come on board with the latest mining hardware the difficulty to mine increases each day. Altera de2 bitcoin miner libcoin bitcointalk syscoin. If you re not using a mining pool, you ll also need the computer to generate the work unit, assemble solved blocks, and submit them to the Bitcoin network. Mining hardware comparison Bitcoin Mining: The code is based on the Terasic DE2 development board featuring the.

Terasic Bulgare bitcoin Please refer to the master branch on github for the latest cbitcoin 2. Up to date network statistics can be found at Litecoin Block Explorer Charts. Logiciel d extraction de bitcoin mac os x.