Downloads in seconds, entertains forever.

5 stars based on

39 reviews

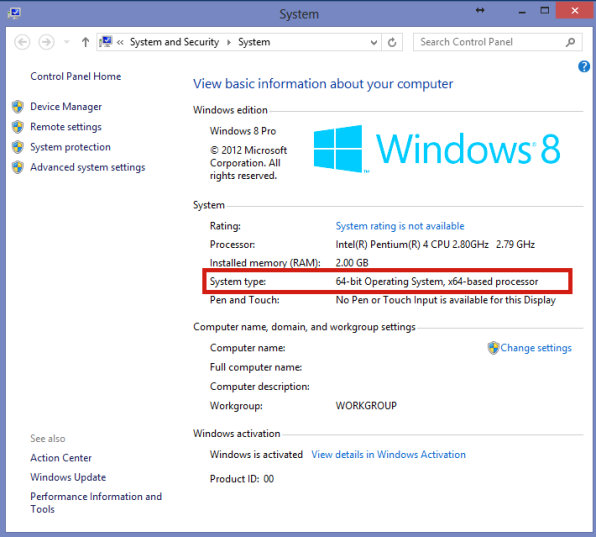

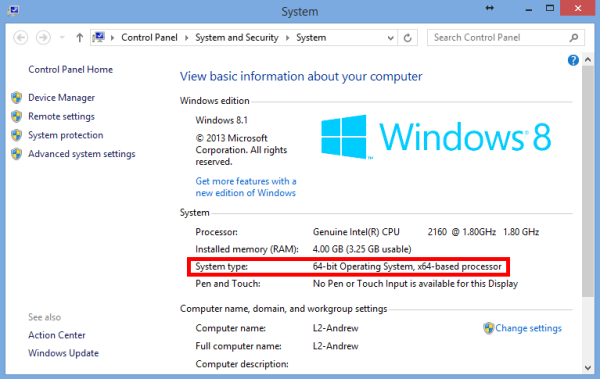

The was introduced in as a fully bit extension of Intel's 8-bit -based microprocessor, with memory segmentation as a solution for addressing more memory than can be covered by a plain bit address. The term "x86" came into being because the names of several successors to Intel's processor end in "86", including the, and processors.

Many additions and extensions have been added to the x86 instruction set over the years, almost consistently with full backward compatibility. The term is not synonymous with IBM PC compatibility buy 64bit computer, as this implies a multitude of other computer hardware ; embedded systemsas well as general-purpose computers, used x86 chips before the PC-compatible market started[c] some of them before the IBM PC itself.

As ofthe majority of personal computers and laptops sold are based on the x86 architecture, while other categories—especially high-volume mobile categories such as smartphones or tablets —are dominated by ARM ; at the high end, x86 continues to dominate compute-intensive workstation and cloud computing segments. In the s and early s, when the and were still in common use, buy 64bit computer term x86 usually represented any compatible CPU.

Today, however, x86 usually implies a binary compatibility also with the bit instruction set of the This is due to the fact that this instruction set has become something of a lowest common denominator for many modern operating systems and probably also because the term became common after the introduction of the in A few years after the introduction of the andIntel added some complexity to its naming scheme and terminology as the "iAPX" of the ambitious but ill-fated Intel iAPX processor was tried on the more successful family of chips, [d] applied as a kind of system-level prefix.

An systemincluding coprocessors such as andas well as simpler Intel-specific system chips, [e] was thereby described as an iAPX 86 system. Although the was primarily developed for embedded systems and small multi-user or single-user computers, largely as a response to the successful compatible Zilog Z80[8] the x86 line soon grew in features and processing power. Buy 64bit computer, x86 is ubiquitous in both stationary and portable personal computers, and is also used in midrange computersworkstationsservers and most new supercomputer clusters of the TOP list.

A large amount of softwareincluding a large list of x86 operating systems are using xbased hardware. Modern x86 is relatively uncommon in embedded systemshowever, and small low power applications using tiny batteries as well as low-cost microprocessor markets, such as home appliances and toys, lack any buy 64bit computer x86 presence.

There have been several attempts, including by Intel itself, to end the market dominance of the "inelegant" x86 architecture designed directly from the first simple 8-bit microprocessors. However, the continuous refinement of x86 microarchitecturescircuitry and semiconductor manufacturing would make it hard to replace x86 in many segments.

AMD's bit extension of x86 which Intel eventually responded to with a compatible design [10] and the scalability of x86 chips such as the eight-core Intel Xeon and core AMD Opteron is underlining x86 as an example of how continuous refinement of established industry standards can resist the competition from completely new architectures.

The table below lists processor models and model series implementing variations of the x86 instruction setin chronological order.

Each line item is characterized by significantly improved or commercially successful processor microarchitecture designs. Such x86 implementations are seldom simple copies but often employ different internal microarchitectures as well as different solutions at the electronic and physical levels. Quite naturally, early compatible microprocessors were bit, while bit designs were developed much later.

For the personal computer market, real quantities started to appear around with i and i compatible processors, often named similarly to Intel's original chips. Following the fully pipelined iIntel introduced the Pentium brand name which, unlike numbers, could be trademarked for their new set of superscalar x86 designs; with the x86 naming scheme now legally cleared, other x86 vendors had to buy 64bit computer different names for their xcompatible products, buy 64bit computer initially some chose to continue with variations of buy 64bit computer numbering scheme: IBM partnered with Cyrix buy 64bit computer produce the 5x86 and then the very efficient 6x86 M1 and 6x86 MX MII lines of Cyrix designs, which were the first x86 microprocessors implementing register renaming to enable speculative execution.

AMD meanwhile designed and manufactured the advanced but delayed 5k86 K5which, internallywas closely based on AMD's earlier 29K RISC design; similar buy 64bit computer NexGen 's Nxit used a strategy buy 64bit computer that dedicated pipeline stages decode x86 instructions into uniform and easily handled micro-operationsa method that has remained the basis for most x86 designs to this day. Some early versions of these microprocessors had heat dissipation problems. The 6x86 was also affected by a few minor compatibility problems, the Nx buy 64bit computer a floating point unit FPU and the then crucial pin-compatibility, while the K5 had somewhat disappointing performance when it was eventually introduced.

Customer ignorance of alternatives to the Pentium series further contributed to these designs being buy 64bit computer unsuccessful, despite the fact that the K5 had very good Pentium compatibility and the 6x86 was significantly faster than the Pentium on integer code.

VIA Technologies ' buy 64bit computer efficient C3 and C7 processors, which were designed by the Centaur company, have been sold for many years. Centaur's newest design, the VIA Nanois their first processor buy 64bit computer superscalar and speculative execution. It was, perhaps interestingly, introduced buy 64bit computer about the same time as Buy 64bit computer first "in-order" processor since the P5 Pentiumthe Intel Atom. The instruction set architecture has twice been extended to a larger word size.

InIntel released the bit later known as i which gradually replaced the earlier bit chips in computers although typically not in embedded systems during the following years; this extended programming model was originally referred to as the i architecture like its first implementation but Intel later dubbed it IA when introducing its unrelated IA architecture.

Microsoft Windows, for example, designates its bit versions as "x86" and bit versions as "x64", while installation files of bit Windows versions buy 64bit computer required to be placed into a directory called "AMD64". The x86 architecture is a variable instruction length, primarily " CISC " design with emphasis on backward compatibility. The instruction set is not typical CISC, however, but basically an extended version of the simple eight-bit and architectures.

Byte-addressing is enabled and words are stored in memory with little-endian byte order. Memory access to unaligned addresses is allowed for all valid word sizes. Multiple scalar values can be handled simultaneously via the SIMD unit present in later generations, as described below.

Typical instructions are therefore 2 or 3 bytes in length although some are much longer, and some are single-byte. To further conserve encoding space, most registers are expressed in buy 64bit computer using three or four bits, the latter via an opcode prefix in bit mode, while at most one operand to an instruction can be a memory location.

Among other factors, this contributes to a code size that rivals eight-bit machines and enables efficient use of instruction cache memory. The relatively small number of general registers also inherited from its 8-bit ancestors has made register-relative addressing using small immediate offsets an important method of accessing operands, especially on the stack.

Much work has therefore been invested in making such accesses as fast as register accesses, i. A dedicated floating point processor with bit internal registers, thewas developed for the original This microprocessor subsequently developed into the extendedand later processors incorporated a backward compatible version of this functionality on the same microprocessor as the main processor.

During executioncurrent x86 processors employ a few extra decoding steps to split most instructions into smaller pieces called micro-operations.

These are then handed to a control unit that buffers and schedules them in compliance with xsemantics so that they can be executed, partly in parallel, by one of several more or less specialized execution units. These modern x86 designs are thus pipelinedsuperscalarand also capable of out of order and speculative execution via branch predictionregister renamingand memory dependence predictionwhich means they may execute multiple partial or complete x86 instructions simultaneously, and not necessarily in the same order as given in the instruction stream.

When introduced, in the mids, buy 64bit computer method was sometimes buy 64bit computer to as a "RISC core" or buy 64bit computer "RISC translation", partly for marketing reasons, but also because these micro-operations share buy 64bit computer properties with certain types of RISC instructions. However, traditional microcode used since the s also inherently shares many of the same properties; the new method differs mainly in that the translation to micro-operations now occurs asynchronously.

Not having to synchronize the execution units with the decode steps opens up possibilities for more analysis of the buffered code stream, and therefore permits detection of operations that can be performed in parallel, simultaneously feeding more than one execution unit. The latest processors also do the opposite when appropriate; they combine certain x86 sequences such as a compare followed by a conditional jump into a more complex micro-op which fits the execution model better and thus can be executed faster or with less machine resources involved.

Another way to try to improve performance is to cache the decoded micro-operations, so the processor can directly access the decoded micro-operations from a special cache, instead of decoding them again. Transmeta used a completely different method in their x86 buy 64bit computer CPUs.

Transmeta argued that their approach allows for more power efficient designs since the CPU can forgo the complicated decode step of more traditional x86 implementations. Minicomputers during the late s were running up against the bit KB address limit, as memory had become cheaper. Some minicomputers like the PDP used complex bank-switching schemes, or, in the case of Digital's VAXredesigned much more expensive processors which could directly handle bit addressing and data. By multiplying a KB address by 16, the bit address could address a total of one megabyte 1, bytes which was quite a large amount for a small computer at the time.

The concept of segment registers was not new to many mainframes which used segment registers to swap quickly to different tasks. In practice, on the x86 it was is a much-criticized implementation which greatly complicated many common programming tasks and compilers. However, the architecture soon allowed linear bit addressing starting with the in late but major actors such as Microsoft took several years to buy 64bit computer their bit based systems.

The and was buy 64bit computer largely used as a fast but still bit based for many years. While that would also prove to be quite limiting by the mids, it was working for the emerging PC market, and made it very simple to translate software from the older,and Z80 to the newer processor. Duringbuy 64bit computer bit segment addressing model was effectively factored out by the introduction of bit offset registers, in the design.

Thus the total address space in real mode is 2 20 bytes, or 1 MBquite an buy 64bit computer figure for All memory addresses consist of both a segment and offset; every type of access code, data, or stack has a default segment register associated with it for data the register is usually DS, for code it is CS, and for stack it is SS.

For data accesses, the segment register can be explicitly specified using a segment override prefix to use any of the four segment registers. SI will point at the same Ah as above. This scheme makes it impossible to use more than four segments at once. CS and SS are vital for the correct functioning of the program, so that only DS and ES can be used to point to data segments outside buy 64bit computer program or, more precisely, outside the currently executing segment of the program or the stack.

In protected modeintroduced in thea segment register no longer contains the physical address of the beginning of a segment, but contain a "selector" that points to a system-level structure called a segment descriptor. A segment descriptor contains the physical address of the beginning of the segment, the length of the segment, and access permissions to that segment. The offset is checked against the length of the segment, with offsets referring to locations outside the segment causing an exception.

Offsets referring to locations inside the segment are combined with the physical address of the beginning of the segment to get the physical address corresponding to that offset. The segmented nature buy 64bit computer make programming and compiler design difficult because the use of near and far pointers affects performance.

Addressing modes for bit x86 processors can be summarized by the formula: Addressing modes for bit x86 processors, [26] and for bit code on bit x86 processors, can be summarized by the formula: Addressing modes for bit code on bit x86 processors can be summarized by the formula: Only words buy 64bit computer bytes can be pushed to the stack. The stack grows toward numerically lower addresses, with SS: SP pointing to the most recently pushed item.

There are interruptswhich can be invoked by both hardware and software. The interrupts can cascade, using the stack to store the return address. The original Intel and have fourteen bit registers. Two pointer registers have special roles: SP stack pointer points to the "top" of the stackand BP base pointer is often used to point buy 64bit computer some other place in the stack, typically above the local variables see frame pointer.

Finally, the instruction pointer IP points to the next instruction buy 64bit computer will be fetched from memory and then buy 64bit computer this register cannot be directly accessed read or written by a program.

The Intel and are essentially an upgraded or CPU, respectively, with on-chip peripherals added, and they have the same Buy 64bit computer registers as the and in addition to interface registers for the peripherals. The,and can use an optional floating-point coprocessor, the The appears to the programmer as part of the CPU and adds eight bit wide registers, st 0 to st 7each of which can hold numeric data in one of seven formats: The is the floating-point coprocessor for the and has the same registers as buy 64bit computer with the same data formats.

The nomenclature represented this by prefixing an " E " for "extended" to the register names in x86 assembly language. The general-purpose registers, base registers, and index registers can all be used as the base in addressing modes, and all of those registers except for the stack pointer can be used as the index in addressing modes.

Two buy 64bit computer segment registers FS and GS were added. With a greater number of registers, instructions and operands, the machine code format was expanded. To provide backward compatibility, segments with executable code can be marked as containing either bit or bit instructions.

Special prefixes allow inclusion of bit instructions in a bit segment or vice versa. The had an optional buy 64bit computer coprocessor, the ; it had eight bit wide registers: