4 stars based on

32 reviews

Digital multipliers are widely used in the arithmetic units of microprocessors, multimedia and digital signal processors.

The main aim of this research work is to design high performance multipliers using different radix to different adders. Modified booth encoding technique is used in this proposed design, where extra partial products are reduced to half. Therefore, the accumulation stages are reduced. 4 bit ripple carry adder block diagram of communication this design, it significantly improves speed, area and delay which is a main objective and purpose of the study.

Modified booth encoding technique improves the power delay product by using different types of adders with different radix such as radix-4, radix-8, and radix The used adders are ripple carry adder and carry look-ahead 4 bit ripple carry adder block diagram of communication, where these are used to know the exact difference by their comparison in terms of delay and area by using Xilinx ISE Digital multipliers are widely used with constant growth of computer applications, fast arithmetic circuits, 4 bit ripple carry adder block diagram of communication and digital signal processors.

Multiplication is a basic arithmetic operation widely used in many applications. The perf ormance of computer applications, mostly depends on the performance of multiplication. The important factors in the design or implementation of multipliers are chip area and speed of multiplication.

There is a high demand of high speed multiplications, which require less hardware. Hence, the performance of the multipliers is affected by the multiplication strategy and the type of multiplier used in the application. Various algorithms and architectures have been proposed to design high-speed and low-power multipliers []. Multiplication by digital circuits include three steps. In the first step, partial products are generated; in the second step, all partial products are added by a partial product reduction tree until two partial product rows remain their accumulation.

In the third step, the two partial product rows are added by a fast carry propagation adder. Booth's encoding is employed to design the fast multipliers by reducing the number of partial products [10].

But, the usage of booth encoding encounter problems or difficulties in generating hard multiples, as it increases the time delay. To overcome this problem, modified booth encoding scheme plays a vital role. In booth encoding, the use of radix-4 and radix-8 gives more hard multiples than radix- 16 [11]. By radix-8 and radix, the hard multiples are significantly reduced. Actually, the Booth's algorithm performs the encoding process serially. Hence the modified booth algorithm, which is proposed performs encoding in parallel and is implemented to design fast multiplier.

Ripple carry adder and carry look ahead adder are employed for high speed accumulation [4],[8]. These are the basic adders experimented to know in detail about the design parameters.

The new design by modified booth encoding using high radix becomes feasible with more reduction in the number of partial products. An exemplary comparison on a bit multiplier using the modified booth encoding with high radix consumes very less power, area and delay. High performance multipliers are popular because of its features, high modularity and carry free addition [9].

The proposed method can be applied to a 8-bit, bit, bit and bit multiplier. In this paper, a new modified technique is used in the bit multiplier for three different radix with the help of adders. There was a brief introduction about radix multiplication which explains radix-4 deeply radix-4, radix-8, radix and the modified booth encoding is given in Section 1.

Section 2, gives the description about 4 bit ripple carry adder block diagram of communication adders used. The speed enhancement and the factors which gives the optimum results are encountered in Section 3, where the simulation results are obtained by the Xilinx ISE The analysis and results are shown in Section 4.

The conclusion about the paper is given in the last. High radix multipliers may be designed to reduce the number of adders and hence the delay required to compute the partial sums. The best method is booth recoding radix-4 [7].

4 bit ripple carry adder block diagram of communication 1, gives the illustration of radix-4 dot notation. To booth recode the multiplier term, we consider bits in block of three as in radix-4, such that each block overlaps the previous block by one bit. Grouping starts from LSB and the first block uses only the two bits of multiplier. Therefore, by the radix booth algorithm, the number of partial products are reduced by half, while keeping the circuit complexity down to a minimum.

Table 1, shows the modified booth encoding scheme of radix Since A represents its multiplicand. Table 2, shows the RB encoding used in this design. For 0,0the RB Digit is '0'.

Similarly, according to the table, the values are assigned for the implementation. The existing low power consuming Booth Encoder Multiplier is developed with the encoder and decoder architecture as shown in Figure 2 and the new MBE scheme is shown in Figure 3 [13].

Table 4, shows the booth recoding values for the proposed architecture. The latest Booth Encoder Multiplier enriched with the 8X8 bit multiplier has given the increased performance than other previous systems [6]. The following partial product array illustrates the details for instance in Figure 4. Since by the proposed modified booth encoding scheme, the array of partial products are reduced by half. Thereby, reducing the accumulation stages. Figure 5, shows the modified booth encoding system, where the adder block plays a vital role [5].

Various adder structures have been frequently used in digital era, with each of them having its superior advantages and unique characteristics in terms of 4 bit ripple carry adder block diagram of communication area, delay and power consideration.

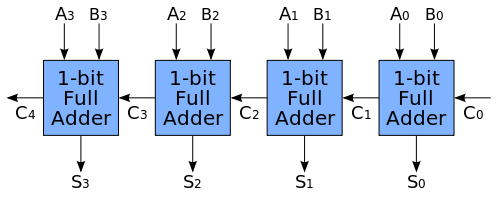

Two adders used in this implementation are ripple carry adder and carry look ahead adder. The Ripple Carry Adder is the basis of any other adder structures, since it is simply composed of n-bit full adders that are connected in series [12]. From which, we have the full adder gate level logic functions as. The functionality of a full adder can easily be obtained from its truth table, shown in Figure 6. For a n-bit ripple carry adder, the block diagram is shown in Figure 7. The disadvantage of the ripple carry adder is that, it is very slow when many bits are added.

The Carry Look-ahead Adder solves this problem by pre-calculation of the carry signals, based on the 4 bit ripple carry adder block diagram of communication signals [2]. It is based on the fact that a carry signal will be generated in two cases:. Notice that, the Propagate and Generate terms only depend on the input bits and, thus, will be valid after two and one gate delay, respectively. If the below equation is used to calculate the carry signals, one does not need to wait for the carry to ripple through all the previous stages to find its proper value.

Hence, the carry for each bit is computed independently. As an example, let's consider a 4-bit adder. In this way, the carry of a n-bit carry lookahead adder can be recursively written as. The analysis is based on the VHDL implementation and the comparison of results of each kind adder structure is explained in Table 5. The analysis is performed in terms of area, speed for the two types of adders, knowing their delay and area by using XilinxISE It is easy to understand that the circuit area increases as the word length the number of bits of an adder increase.

Of the two adders, the results show that at the gate level, the sequence from the smallest area to the largest area is RCA and CLA. Obviously, ripple carry adder has the least chip area because of its simplicity in structure. CLA is the most area consuming. The speed of adders is very important for any ASIC design. In radix, the delay is very less when compared with radix-4 and radix In the case without pipeling, when the input bits are doubled or tripled, the delay of RCA is approximately doubled or tripled as well, which cannot be practically used.

CLA is speed improving compared with RCA, by using their particular structure to shorten the critical path. CSA is independent of input bits and behaves as a full adder in speed, and thus the fastest one in other adders.

The obtained results have been evaluated. A new modified booth encoding scheme is proposed in this paper, and this design eliminates the unnecessary hard multiples by using high radix such as radix-8 and radix Through the use of ripple carry adder and carry look-ahead adder, it is easy to compare the performance of the multipliers with different types of radix.

It is proven that, the delay and area are improved in that carry lookahead adder when compared with ripple carry adder. Therefore, the proposed design with different radix induce that delay and area factors are significantly improved. Hence, the modified booth encoding scheme 4 bit ripple carry adder block diagram of communication highly used for high performance multipliers. Further, this paper can be extended for other type of adders like carry save adder and carry select adder, which gives high performance in terms of speed and area for implementing the modified partial product generations.

Abstract Digital multipliers are widely used in the arithmetic units of microprocessors, multimedia and digital signal processors. Modified Booth Encoding Scheme. Booth Recoding Values of Radix Modified Booth Encoding System. Swartzlander, and Fabrizio Lombardi, Amita, and Nithin Sachdeva, R Usha Rani, Journal of Computer Applications, Vol.