4 bit ripple carry adder using full adder truth

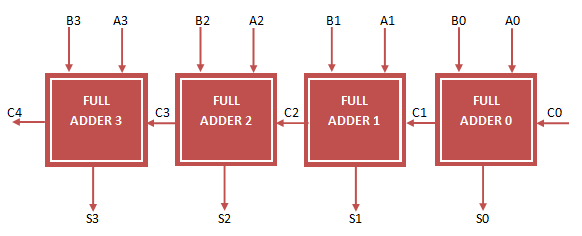

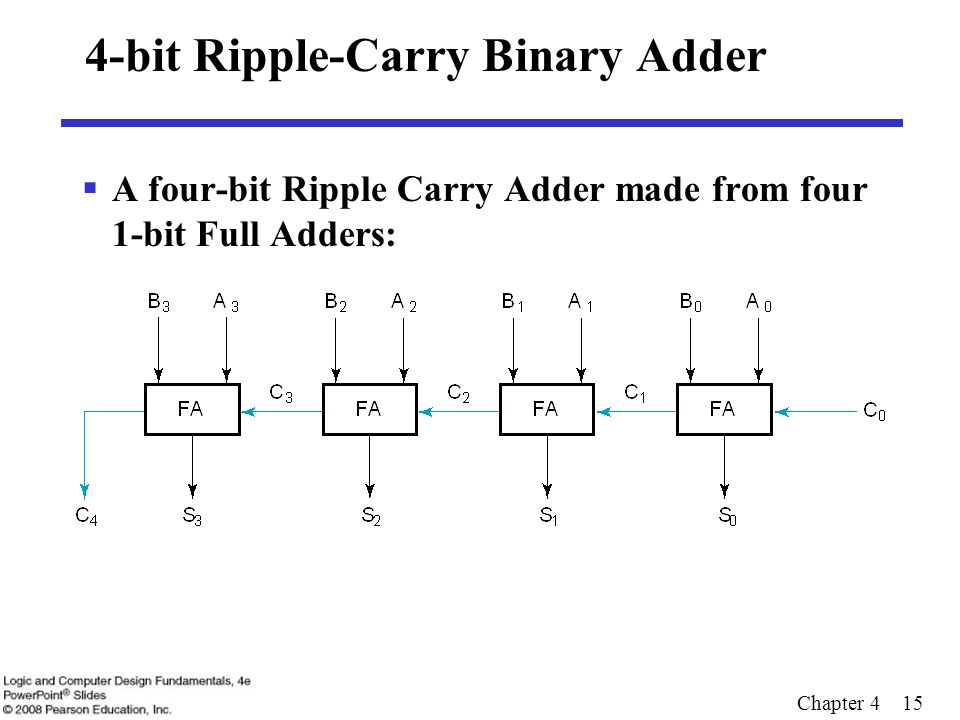

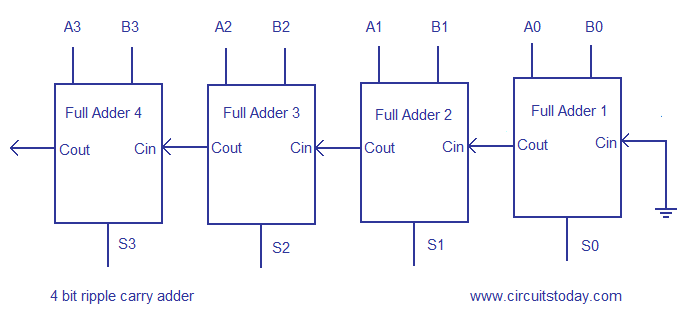

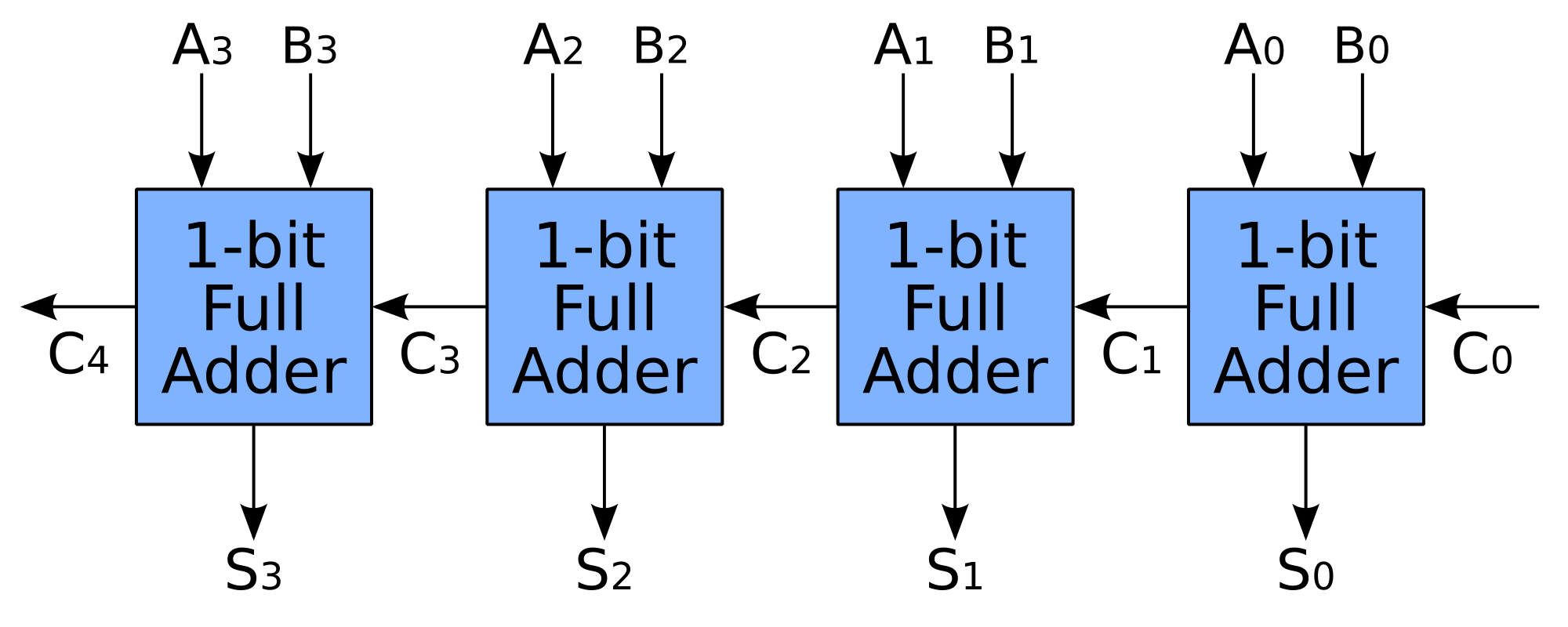

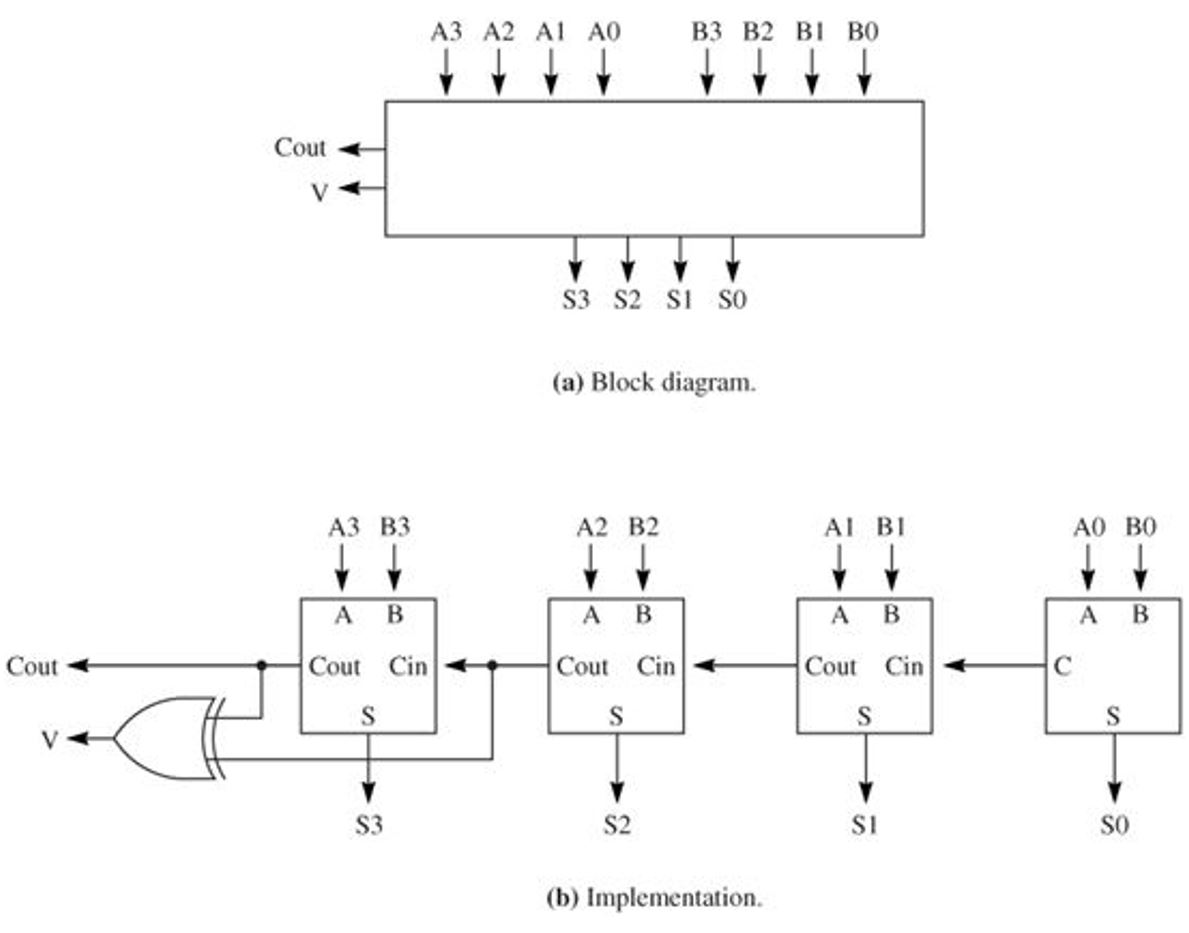

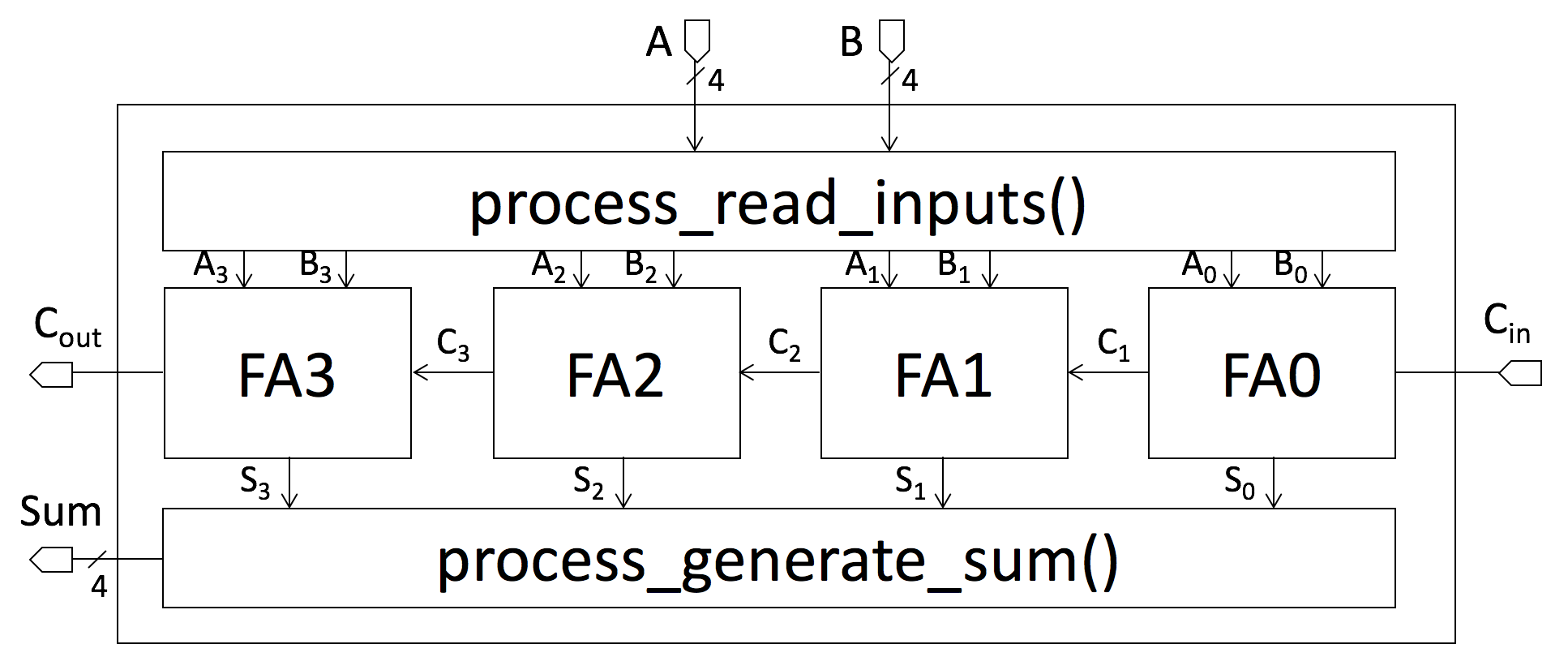

The output variables are the sum and carry. With the addition of an OR gate to combine their carry outputs, two half adders can be combined to make a full adder. These block based adders include the carry-skip or carry-bypass adder which will determine P and G values for each block rather than each bit, and the carry select adder which pre-generates the sum and carry values for 4 bit ripple carry adder using full adder truth possible carry input 0 or 1 to the block, using multiplexers to select the appropriate result when the carry bit is known. After P and G are generated, the carries for every bit position are created. Such compressors can be used to speed up the summation of three or more addends.

In other projects Wikimedia Commons. Some other multi-bit adder architectures break the adder into blocks. Assumed that an XOR-gate takes 1 delays to complete, the delay imposed by the critical path of a full adder is equal to.

These block based adders include the 4 bit ripple carry adder using full adder truth or carry-bypass adder which will determine P and G values for each block rather than each bit, and the carry select adder which pre-generates the sum and carry values for either possible carry input 0 or 1 to the block, using multiplexers to select the appropriate result when the carry bit is known. Views Read Edit View history. A full adder can be implemented in many different ways such as with a custom transistor -level circuit or composed of other gates. If an adding circuit is to compute the sum of three or more numbers, it can be advantageous to not propagate the carry result.

In other projects Wikimedia Commons. Retrieved from " https: An adder is a digital circuit that performs addition of numbers.

A full adder can be viewed as a 3: The sum and the carry may be fed into two inputs of the subsequent 3-number adder without having to wait for propagation of a carry signal. In this implementation, the final OR gate before the carry-out output may be replaced by an XOR gate without altering the resulting logic.

Such compressors can be used to speed up the summation of three or more addends. If an adding circuit is to compute the sum of three or more numbers, it can be advantageous to not propagate the carry result. The gate delay can easily be calculated by inspection of the full adder circuit.

A full adder adds binary numbers and accounts for values carried in as well as out. Likewise, a half adder can be used as a 2: Each full adder requires three levels of logic. The gate delay can easily be calculated by inspection of the full adder circuit.

Other signed number representations require more logic around the 4 bit ripple carry adder using full adder truth adder. This kind of circuit is most notably used in multipliers, which is why these circuits are also known as Dadda and Wallace multipliers. By combining multiple carry-lookahead adders, even larger adders can be created. After all stages of addition, however, a conventional adder such as the ripple-carry or the lookahead must be used to combine the final sum and carry results. Although adders can be constructed for many number representationssuch as binary-coded decimal or excess-3the most common adders operate on binary numbers.

The output variables are the sum and carry. This can be used at multiple levels to make even larger adders. Such compressors can be used to speed up the summation of three or more addends. The circuit produces a two-bit output. In most cases, P is simply the sum output of a half adder and G is the carry output of the same adder.