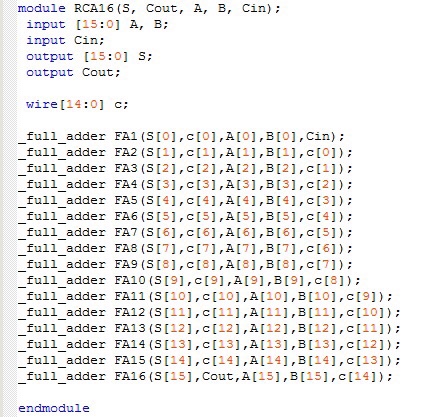

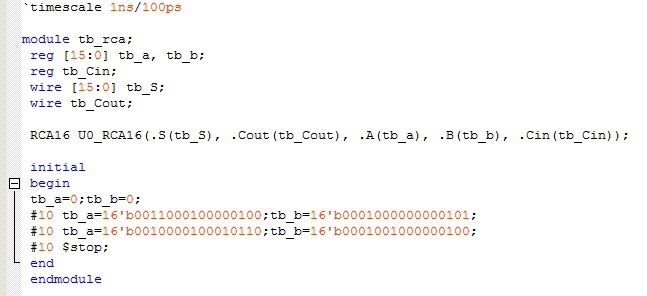

Verilog code for 16 bit ripple carry adder vhdl

Moreover, if the sum without a carry is 9 in pencil-and-paper methods or 1 verilog code for 16 bit ripple carry adder vhdl binary arithmeticit is not even possible to tell whether or not a given digit position is going to pass on a carry to the position on its left. It can be contrasted with the simpler, but usually slower, ripple-carry adder RCAfor which the carry bit is calculated alongside the sum bit, and each bit must wait until the previous carry bit have been calculated to begin calculating its own result and carry bits. Passages from the Life of a Philosopher.

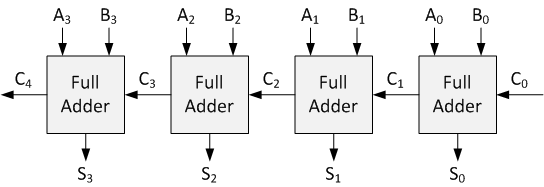

From Wikipedia, the free encyclopedia. This page was last edited on 1 Mayat A full adder is a combinational verilog code for 16 bit ripple carry adder vhdl that takes 3 bits, aband carry-inand outputs their sum, in the form of two bits, carry-outand sum. Finally, within each group that receives a carry, the carry propagates slowly within the digits in that group. A ripple-carry adder works in the same way as pencil-and-paper methods of addition.

It is the "rippling" of the carry from right to left that gives a ripple-carry adder its name, and its slowness. This lab should be done after the introduction lab on Verilog. Views Read Edit View history.

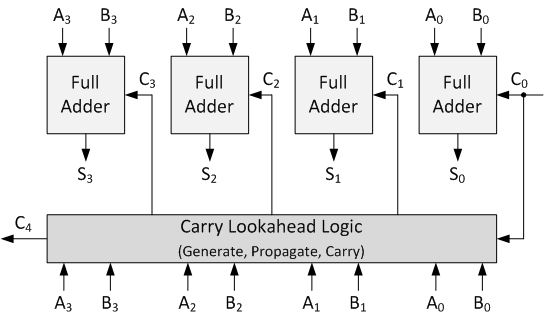

As can be seen above in the implementation section, the logic for generating each carry contains all of the logic used to generate the previous carries. This allows the circuit to "pre-process" the two numbers being added to determine the carry ahead of time. The more bits in a group, the more complex the lookahead carry logic becomes, and the more time is spent on the "slow roads" in each group rather than on the "fast road" between the groups provided by the lookahead carry logic.

The addition of two 1-digit inputs A and B is said to generate if the addition will always carry, regardless of whether there is an input-carry equivalently, regardless of whether any less significant digits in the sum carry. The XOR is used normally within a basic full adder circuit; the OR is an alternative option for a carry-lookahead onlywhich is far simpler in transistor-count terms. Carry-lookahead logic uses the concepts of generating and propagating carries.

The carry-lookahead 4-bit adder can also verilog code for 16 bit ripple carry adder vhdl used in a higher-level circuit by having each CLA logic circuit produce a propagate and generate signal to a higher-level CLA logic circuit. The timing diagram is fine, but a bit hard to read. The addition of two 1-digit inputs A and B is said to generate if the addition will always carry, regardless of whether there is an input-carry equivalently, regardless of whether any less significant digits in the sum carry. However, not all logic families have these internal nodes, CMOS being a major example.

The idea is simple. This lab should be done after the introduction lab on Verilog. In the case of binary addition, this definition is expressed by. For the example provided, the logic for the generate g and propagate p values are given below. A Manchester-carry-chain section generally doesn't exceed 4 bits.