3 bit up down ripple counters

The result is called a ripple counter, which can count to 2 n - 1 where n is the number of bits flip-flop stages in the counter. This 3 bit up down ripple counters will increment once for every clock cycle and takes two clock cycles to overflow, so every cycle it will alternate between a transition from 0 to 1 and a transition from 1 to 0. Numeral systems Digital circuits Unary operations. In other projects Wikimedia Commons. Once set up, these counters will be incremented by one every time the web page is accessed in a web browser.

Ripple counters suffer from unstable outputs as the overflows "ripple" from stage to stage, but they do find frequent application as dividers for clock signals, where the instantaneous 3 bit up down ripple counters is unimportant, but the division ratio overall is to clarify this, a 1-bit counter is exactly equivalent to a divide by two circuit; the output frequency is exactly half that of the input when fed with a regular train 3 bit up down ripple counters clock pulses. An ordinary four-stage counter can be easily modified to a decade counter by adding a NAND gate as in the schematic to the right. This page was last edited on 3 Mayat You can continue to add additional flip-flops, always inverting the output to its own input, and using the output from the previous flip-flop as the clock signal. Long before electronics became common, mechanical devices were used to count events.

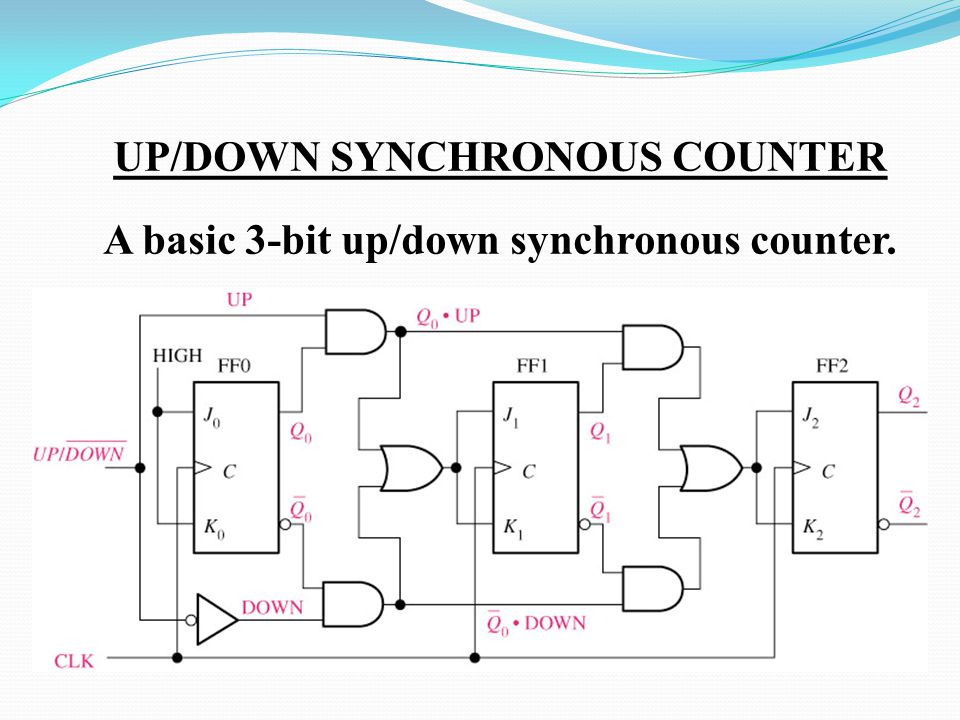

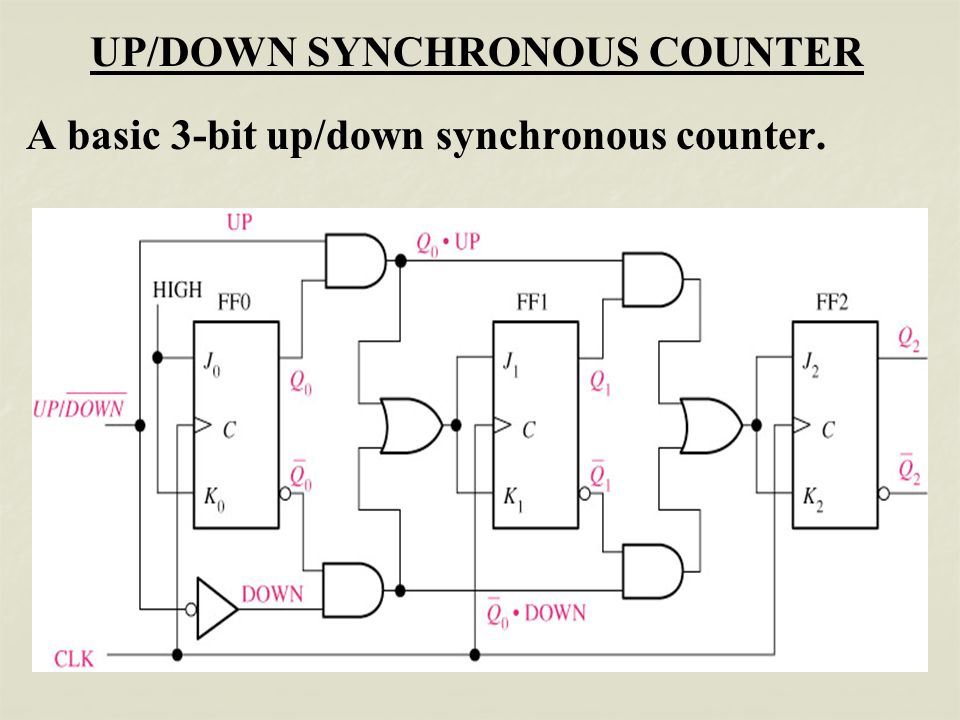

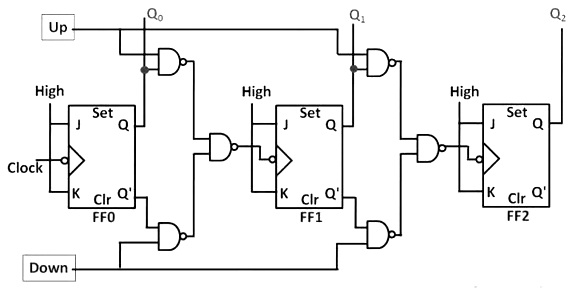

The first machine, an FSM plus two counters, is equivalent in power to a Turing machine. The circuit below is a 4-bit synchronous counter. A ring counter is a circular shift register which is initiated such that only one of its flip-flops is the state one while others are in their zero states.

Usually, counter circuits are digital in nature, and count in natural binary. Counters may count parameters such as the number of pieces produced, the production batch number, and measurements of the amounts of material used. The first two and the last one are levels of the Chomsky hierarchy.

A web counter or hit counter is a computer software program that indicates the number of visitors, or hits, a particular webpage has received. Once set up, these counters will be incremented by one every time the web page is accessed in a web browser. For the first and last, it doesn't matter whether the FSM is a deterministic finite automaton or a nondeterministic finite automaton. Synchronous counters can also be implemented with hardware finite-state machineswhich are more complex but 3 bit up down ripple counters for smoother, more stable transitions. Views Read Edit View history.

For example, bit 1 toggles when bit 3 bit up down ripple counters is logic high; bit 2 toggles when both bit 1 and bit 0 are logic high; bit 3 toggles when bit 2, bit 1 and bit 0 are all high; and so on. Images may be presented in a variety of fontsor styles; the classic example is the wheels of an odometer. Each disk except the left-most has a protrusion that, after the completion of one revolution, moves the next disk to the left one increment.

Thus, all the flip-flops change state simultaneously in parallel. The right most disk moves one increment with each event. Numeral systems Digital circuits Unary operations.

The right most disk moves one increment with each event. For example, bit 1 toggles when bit 0 is logic high; bit 2 toggles when both bit 1 and bit 0 are logic high; bit 3 toggles when bit 2, bit 1 and bit 0 are all high; and so on. Web counter was popular in the mid to 3 bit up down ripple counters s and early s, later replaced by more detailed and complete web traffic measures.

The result is that the NAND output goes low, and resets the counter to zero. Each disk except the left-most has a protrusion that, after the completion of one revolution, moves the 3 bit up down ripple counters disk to the left one increment. This counter will increment once for every clock cycle and takes two clock cycles to overflow, so every cycle it will alternate between a transition from 0 to 1 and a transition from 1 to 0.

It counts from 0 to 9 and then resets to zero. Usually, counter circuits are digital in nature, and count in natural binary. Typically, a pattern consisting of a single bit is circulated so the state repeats every n clock cycles if n flip-flops are used. In other projects Wikimedia Commons.